一般信息

产品编号:编号:3AST000929R109

ABB型号名称:DAPI 100

目录说明:DAPI 100 以太网通信器接口

详细描述:以太网 MVI

类别

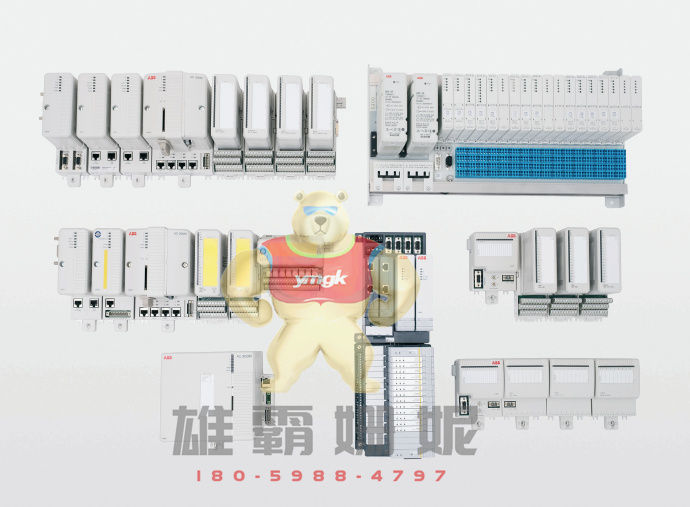

产品 » 控制系统产品 » 控制与 通信 » AC 400 » AC 400 - 通信模块 » DAPI 100 以太网接口 » DAPI 100 以太网接口

以太网接口是用于连接以太网线的接口,它通常由MAC(媒体接入控制器)和PHY(物理接口收发器)组成。

MAC是由IEEE 802.3以太网标准定义的,它实现了数据链路层。常用的MAC支持10Mbit/s或100Mbit/s两种速率。MAC和PHY之间采用MII(媒体独立接口)连接,它是IEEE-802.3定义的以太网行业标准,包括1个数据接口与MAC和PHY之间的1个管理接口。MII管理接口包含两个信号,一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制PHY。

3AST000929R109一个以太网接口的硬件电路原理如下图所示,从CPU到最终接口依次为CPU、MAC、PHY、以太网隔离变压器、RJ45插座。许多处理器内部集成了MAC或同时集成了MAC和PHY,另有许多以太网控制芯片也集成了MAC和PHY。

3AST000929R109以太网接口的主要作用是将MAC层数据(MII接口数据)通过串并转换器,重新排序,并根据响应的调制方式,将信号重新编码,再通过MDI接口(介质相关接口)将数据通过对应线路传送出去。具体过程是PCS(物理编码)子层位于协调自曾(通过GMII)和物理介质接入层子层之间。PCS完成将经过完善定义的以太网MAC功能映射到现存的编码和物理层信号系统的功能上去。

General information

Product Number: Number: 3AST000929R109

ABB model name: DAPI 100

Directory Description: DAPI 100 Ethernet communicator interface

Description: Ethernet MVI

category

Products » Control System Products » Control and Communication » AC 400 » AC 400 - Communication Module » DAPI 100 Ethernet interface » DAPI 100 Ethernet interface

An Ethernet interface is an interface used to connect an Ethernet cable, which usually consists of a MAC (Media Access controller) and a PHY (physical interface transceiver).

The MAC is defined by the IEEE 802.3 Ethernet standard, which implements the data link layer. A common MAC supports 10Mbit/s or 100Mbit/s. The MAC and PHY are connected using MII (Media Independent Interface), which is the Ethernet industry standard defined by IEEE-802.3 and includes a data interface and a management interface between the MAC and PHY. The MII management interface contains two signals, one is a clock signal and the other is a data signal. Through the management interface, the upper layer can monitor and control the PHY.

The following figure shows the hardware circuit principle of 3AST000929R109 Ethernet interface. From the CPU to the final interface, the hardware circuit consists of CPU, MAC, PHY, Ethernet isolation transformer, and RJ45 socket. Many processors have MAC or both integrated, and many Ethernet control chips also have MAC and PHY integrated.

The main role of the 3AST000929R109 Ethernet interface is to reorder the MAC layer data (MII interface data) through the series parallel converter, and according to the modulation mode of the response, the signal is re-encoded, and then the data is transmitted through the corresponding line through the MDI interface (media related interface). The process is that the PCS (Physical coding) sublayer is located between the coordinating self layer (via GMII) and the physical media access layer sublayer. PCS completes the mapping of well-defined Ethernet MAC capabilities to existing coding and physical-layer signaling systems.

| BLACK BOX | ACR1000A-R2 | |

| TRICONEX | 3504E | |

| ABB | 3BDH000741R1 | |

| HONEYWELL | TK-CCR014 | |

| WOODHEAD | DRL-DPM-BKF | |

| Rolls-Royce | SLIO 02 | |

| WOODWARD | 9905-973 | |

| A-B | 2711P-B6C20D | |

| PROSOFT | MVI56-BAS | |

| ABB | 3BUS208800-001 | |

| HONEYWELL | FC-SDO-0824 V1.3 | |

| EL AU | C200/10/1/1/100 | |

| VIBRO-METER | 200-510-076-114 200-510-111-034 VM600 MPC4 | |

| ICS TRIPL EX | T8431 | |

| SCANL AB | INTELLISCANDE I14-532NM SCANL AB |

Copyright © 2022-2024 厦门雄霸电子商务有限公司 版权所有 备案号:闽ICP备14012685号-33